Applications

There has been an ever-increasing need for higher speed and

lower power dissipation in high resolution analog-to-digital

converters. These converters find application in areas such

as wireless communications, high-energy physics, and measurement

and instrumentation equipment. In recent years, switched-

capacitor pipelined converters have emerged as an especially

attractive architecture for implementing Nyquist-rate quantizers

for medium to high resolution conversion with medium to high

conversion rates and reasonable power consumption. Floating-

point A/D converters have been shown to be useful in high

resolution applications in which the least significant bits are

not used when encoding large signals. Floating-point analog-to-

digital converters (FADC) employ nonuniform quantization and

typically dissipate less power and require less hardware than

comparable uniform quantizers. Due to the nonuniform nature of

the quantization, FADCs sacrifice a large peak signal-to-noise

ratio (SNR) for an increase in dynamic range. The key objective

in this research is to combine the features of a pipelined

converter and a FADC to reduce power dissipation, strigent

linearity requirements, and calibration complexity for a

high speed, high resolution converter.

Applications

Floating-point analog-to-digital converters have generally been

used for experiments in which the acquired signal is of a non-

repeatable nature such as those caused by explosions, impacts, or

earthquakes in which the initial high amplitude pulse is followed

by a low amplitude ringing component. Moreover, these converters

are useful in large dynamic range applications in high-energy

physics. In particular, floating point converters are utilized

in experiments for electromagnetic calorimeters for detectors

in colliding beam machines. Additionally, nonuniform converters

may be attractive for wireless applications in which low-

amplitude signals must be acquired and processed with a SNR of

40 dB - 70 dB.

Publications

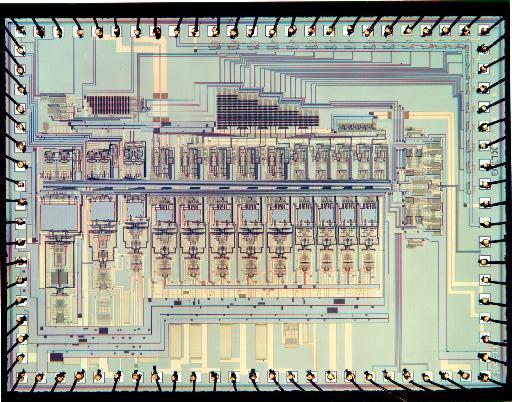

D.U. Thompson, B.A. Wooley, " A

15-bit Pipelined Floating-Point A/D Converter ,"

1999 European Solid-State Circuits Conference Proceedings, Duisburg,

Germany,

pp. 170-173, Sept. 1999.